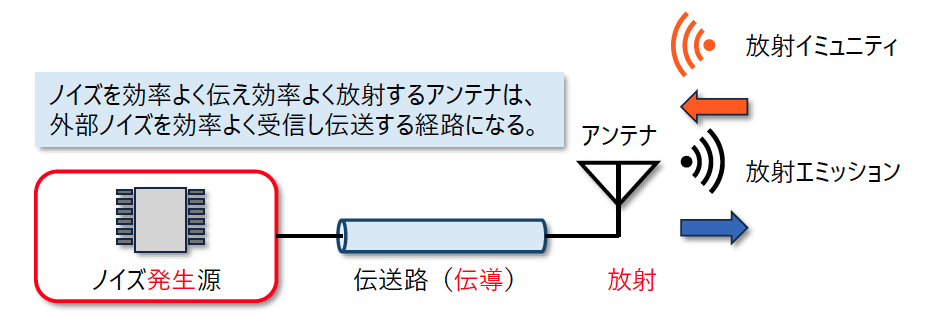

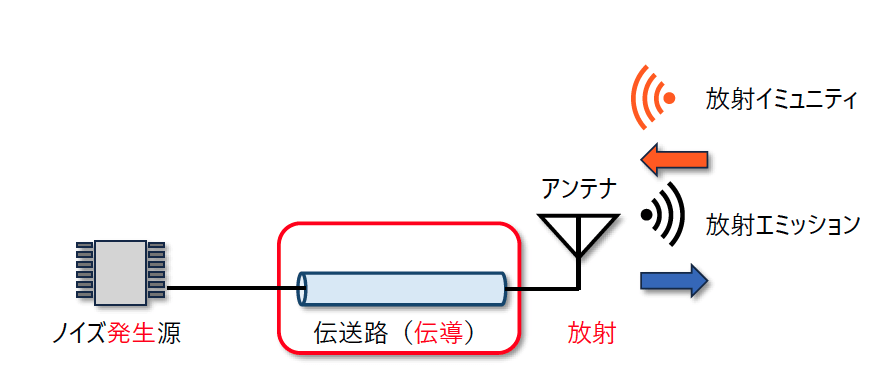

空間に放射されるノイズは、ノイズ発生源→伝送路→アンテナと伝搬し、外部に電磁波として放出される( 「図1 放射ノイズ発生原理」 )。放出された電磁波は他の機器の動作を妨害する。逆に、他の機器から放射された電磁波はこの逆ルートで機器に侵入し、機器の動作を妨害する。放射エミッション対策を施した機器は、他の機器からの影響も受けにくいと言われるのは、この双方向性による。

ノイズ発生源は半導体デバイス、発信器や DC/DC コンバータなどの電源がある。伝送路はプリント基板パターン、筐体内配線や筐体の金属部になる。プリント基板のパターン、筐体内ワイヤー、筐体の金属部や外部ケーブルが意図しないアンテナになる。

電磁波ノイズの放射を抑えるためには、ノイズ発生源と伝送路でノイズレベルを下げることと、極力アンテナを少なくする(効率を下げる)ことが必要だ。

ノイズ発生

ドライバ IC の電流

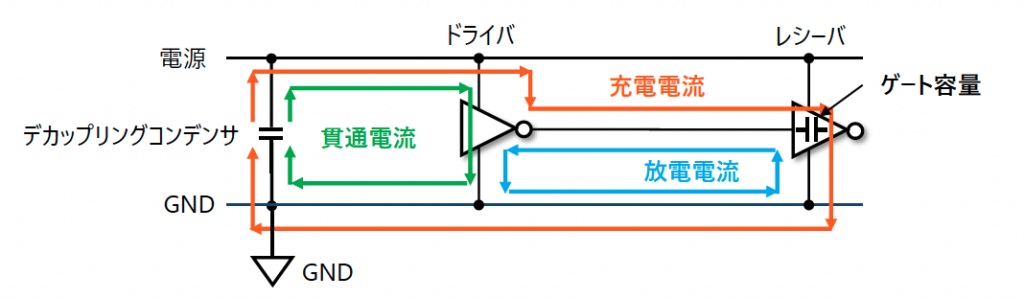

「図2 デジタル回路モデル」は、ドライバとレシーバのシンプルなモデルだ。ドライバを単純なスイッチとみなしている。ドライバが電源につながると、レシーバのキャパシタ(ゲート容量)を充電し High レベルになる。この時橙色の経路で電流が流れる。ドライバが GND につながるとレシーバのキャパシタは放電し青色の経路で電流が流れる。

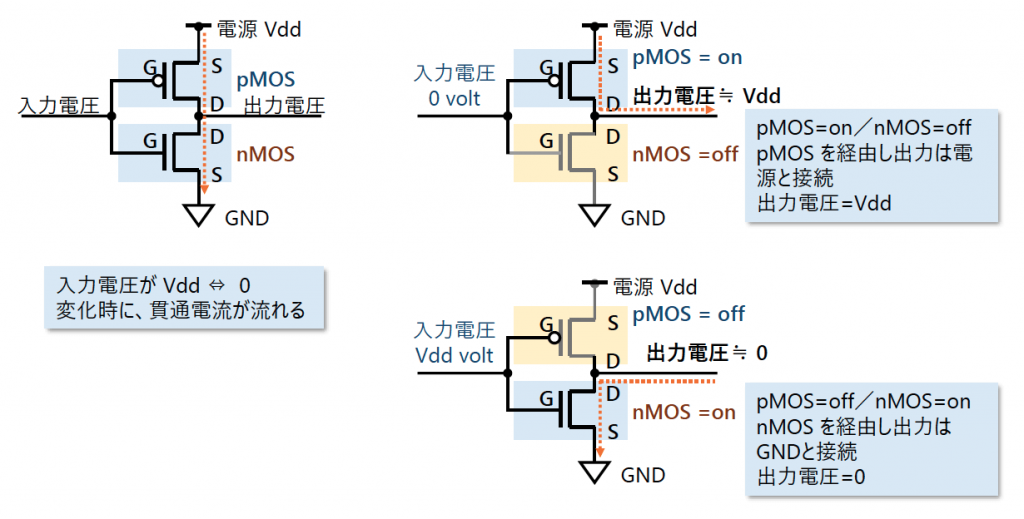

CMOS IC は、ドライバの on/off 切り替え時に、電源と GND が一瞬つながり貫通電流が流れる。緑線の経路で貫通電流が流れる。貫通電流はデカップリングコンデンサを放電する形で流れ、信号の on/off いずれでも同じ方向に流れるため信号周波数の2倍になる。

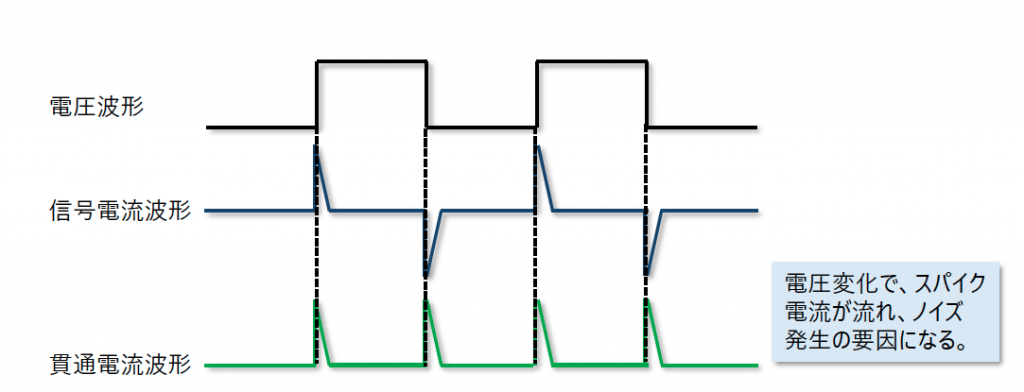

これらのレシーバキャパシタ(ゲート容量)の充放電と、貫通電流で流れるスパイク状の電流がノイズの発生源になる。電圧レベルの変化と、充放電及び貫通電流のイメージは「図3 電圧と電流」を参照いただきたい。

レシーバのゲート容量の充電電流と放電電流は、電圧の立上りと立下りの変化で流れ、CMOS の貫通電流は電圧変化で同方向に流れる。

高調波

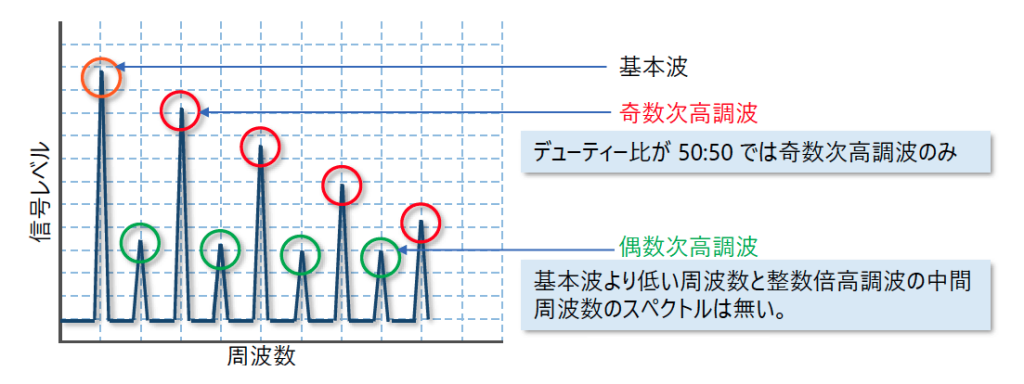

クロック信号の様な一定の周期を繰り返す信号は、繰り返し周波数である「基本波」とその整数倍の周波数である「高調波」に分解できる。基本的には「基本波」と「高調波」以外の周波数は存在しない。クロック信号にジッターがあると、クロックの基本周波数から外れた周波数が登場する。

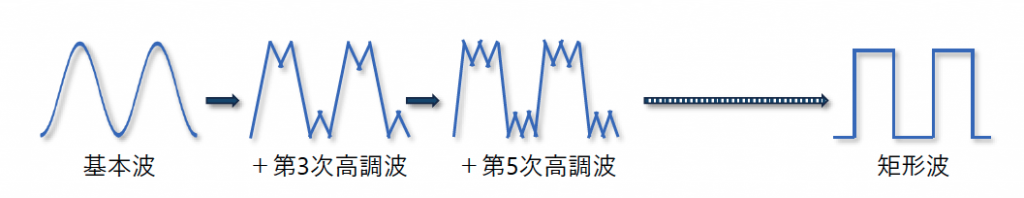

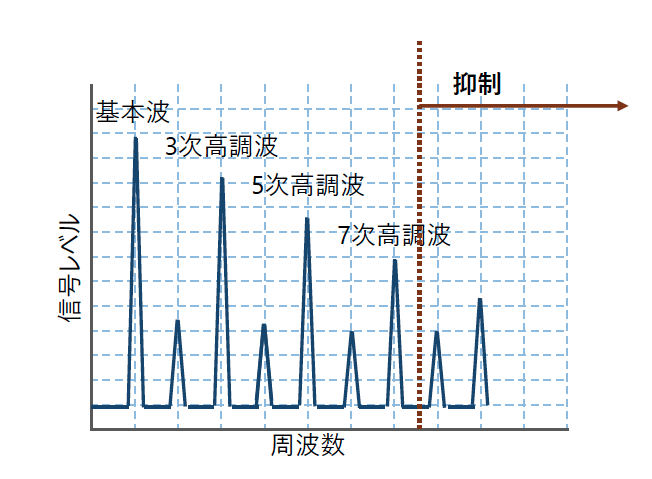

デジタル信号は、基本波に次数の小さい高調波を順次足し込むと矩形波に近づく。逆に矩形波から、順次高次の高調波を削除すると基本波の正弦波に近づく( 「図5 基本波と高調波」 )。デジタル信号は、基本波と次数の低い高調波は信号波形の構成に重要だが、次数の高い高調波はあまり重要ではない。

次数の高い高調波は必然的に周波数が高くなり、電波として外に放射されやすく妨害波になる。ノイズ対策として、信号波形の構成にあまり必要ではない高次の「高調波」を取り除くことになる。一般的には、7倍(7次)程度までの高調波を残し、これ以上の高次高調波をローパスフィルタで取り除くことになる。

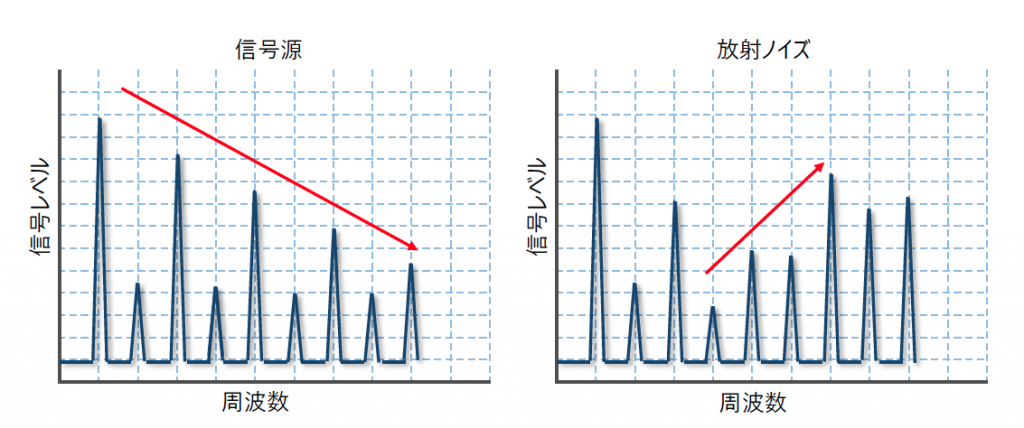

矩形波のデジタル信号は基本波だけではなく、基本波の整数倍の高調波が発生する。信号源に含まれる高調波は周波数が高くなるにつれ減衰するが、周波数が高くなるほど電波として放射されるため、放射ノイズでは周波数の高い高調波のレベルが高くなる傾向がある( 「図6 信号源と放射ノイズ」 )。

クロック信号の様に、一定の繰り返し周期を持つ信号には、元周期の「基本波」とその整数倍の「高調波」がある。正確な周期の信号には、整数倍以外の周波数の高調波な存在しない。

高調波には「奇数次の高調波」と「偶数次の高調波」がある。デューティー比が 50:50 の繰り返し波形では、奇数次高調波のみが存在し偶数次高調波は無い。デューティー比が 50:50 から外れると、偶数次の高調波が発生する( 「図7 高調波」 )。

この特性から、基本波の周波数が分かれば発生源を特定することができる。複数基本波の最小公倍数の周波数は、複数の高調波が重なる。

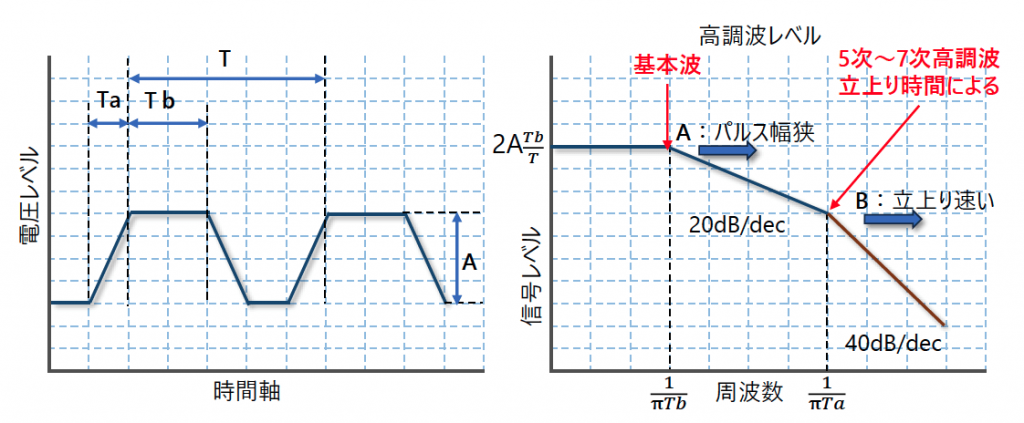

矩形波の高調波レベルは 2 つの変曲点を持つ特性がある。 A 点はパルス幅で決まる変曲点で、パルス幅が狭くなるほど高周波側(右)に移動する。 B 点は立上り/立下り時間で決まる変曲点で、立上り/立下り時間が早いほど高周波側(右)に移動する( 「図8 高調波包絡線」 )。理想的には、低周波側に移動するほうがノイズを抑制できるが、デジタル回路の高速化に伴い高周波側に移動し、ノイズ抑制が難しくなる傾向にある。

EMI 対策では、基本的には 7 次高調波を超える周波数を抑制する( 「図9 EMI 対象高調波」 ) 。

ノイズ伝導

半導体デバイス、発信器やDC/DC コンバータ等で発生したノイズは、伝送路を通りアンテナから放射される。伝送路はプリント基板パターン、筐体内配線や筐体の金属部になる。プリント基板のパターン、筐体内配線や筐体の金属部が意図しないアンテナになる( 「図10 放射ノイズ発生原理」 )。

発生したノイズを放射しないためには、伝送路でのノイズ伝送や増幅を抑える必要がある。

発生したノイズを放射しないためには、伝送路でのノイズ伝送や増幅を抑える必要がある。

反射

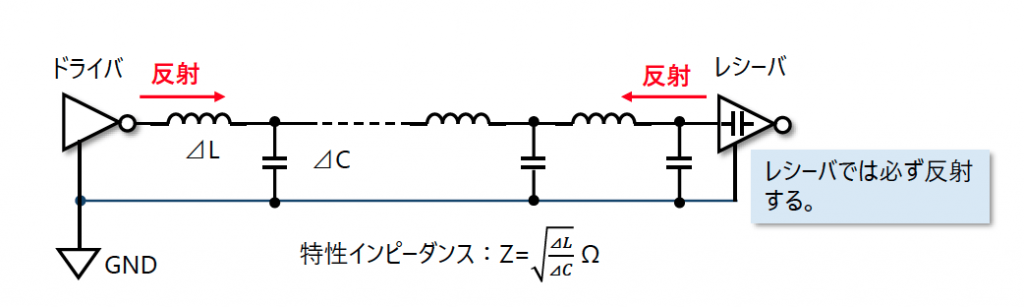

ドライバとレシーバ間の伝送線路には特性インピーダンスがある。「図11 分布定数線路」の様に、単位長さ当りのインダクタンスと静電容量により特性インピーダンスは決まる(実際は純抵抗もあるが省略)。通常伝送線路の特性インピーダンスは 50Ω 150Ω 程度だ。

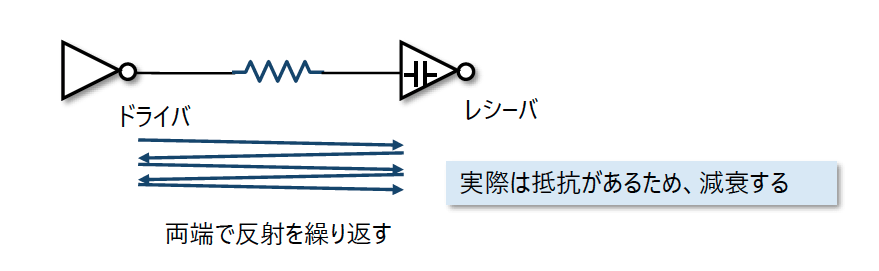

レシーバのインピーダンスが伝送線路の特性インピーダンスと等しいときは、電気エネルギーは負荷側で吸収され反射は無い。負荷側のインピーダンスが伝送線路の特定インピーダンスと異なるとき、信号は反射する。デジタル IC の入力インピーダンスは数100Ω(もちろん周波数に依存)と高く、レシーバで反射する。ドライバの出力インピーダンスは様々だが、ここでも反射している可能性が高い。つまり、デジタル信号は信号線の両端で反射を繰り返すことになる。

ドライバとレシーバの両方で反射し多重反射が起きると、伝送線路が共振器になり、リンギングが起きる( 「図12 リンギング発生の仕組み」 )。

リンギング

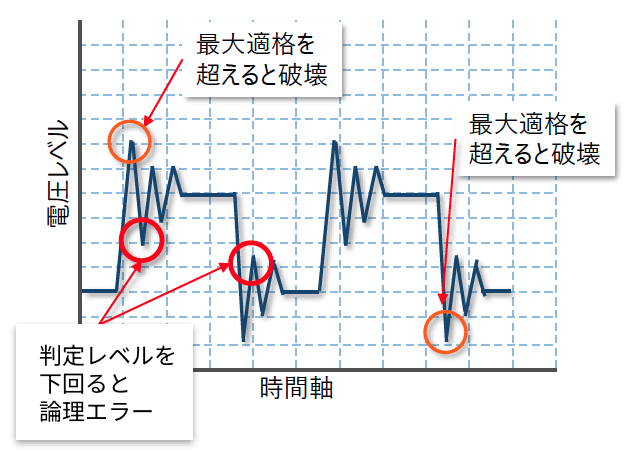

リンギングが発生するとこれに伴い高調波が発生する。信号線が長くなると共振が発生しやすくなる傾向があり、デジタル回路の誤動作を引き起こす可能性もある( 「図13 リンギング」 )。

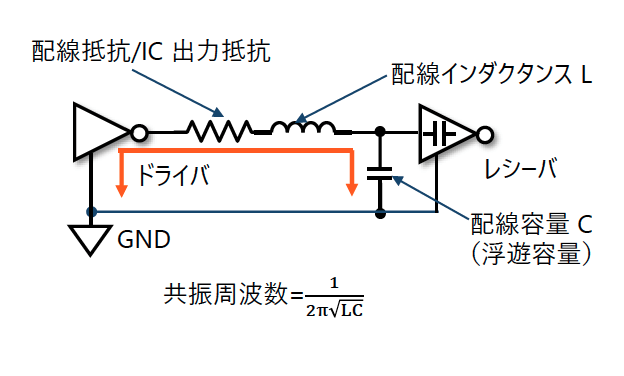

リンギングは、配線のインダクタンスとキャパシタンス(静電容量)により共振回路が作られるためだ。「図14 デジタル回路モデル」では、配線の持つインダクタンスと静電容量で共振する例だ。

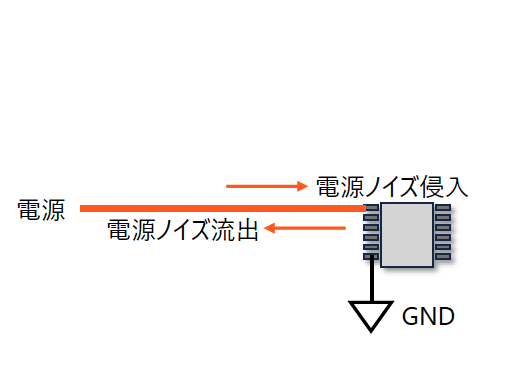

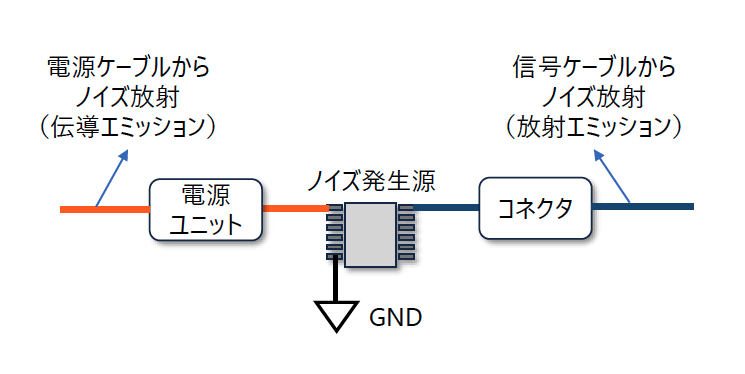

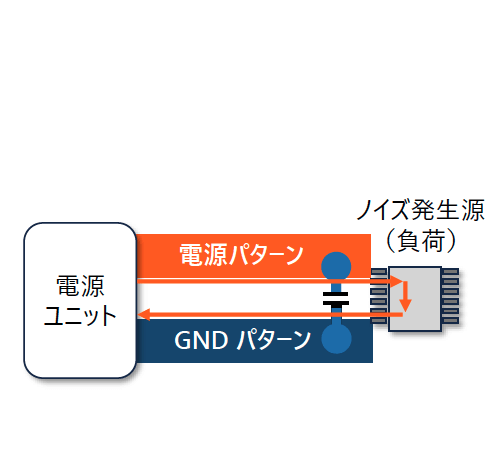

電源変動

電源や GND は様々な回路の共有部になる。電源や GND はデジタル IC で発生したノイズが流れ込んだり、電源 GND のノイズがデジタル IC に侵入する経路になる( 「図15 電源ノイズの侵入と流出」 )。電源 GND にノイズが流れ込むと装置全体に影響が出る。電源や GND のノイズ(電圧変動)は、電源ケーブルや信号ケーブルを介して、外部に放出され妨害波になる( 「図16 外部ケーブル放射」 )。

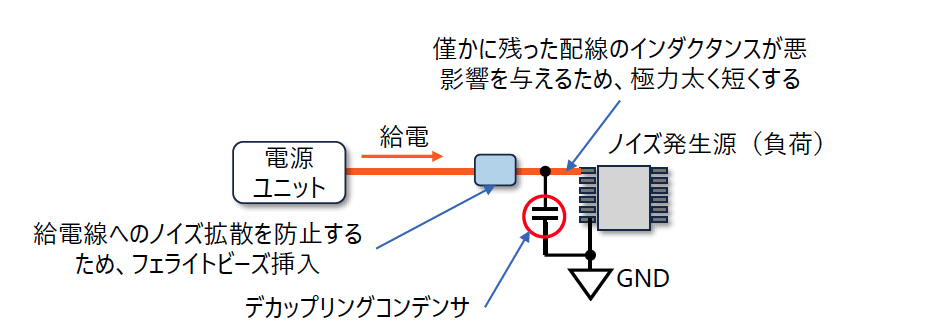

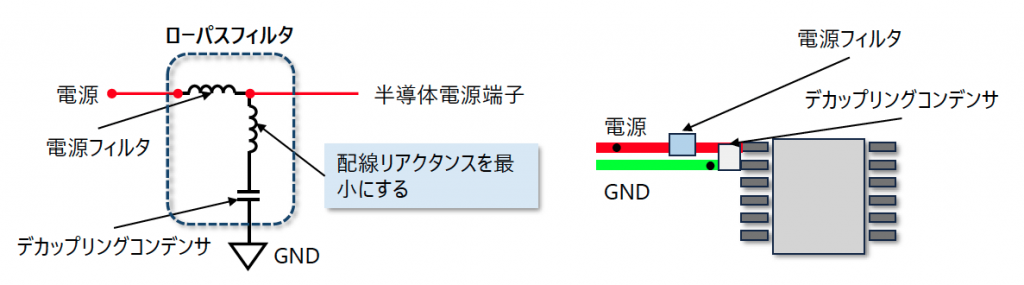

電源とノイズ発生源(負荷)を接続する配線にはインダクタンスがある。特に高周波では配線のインダクタンスがインピーダンスを増大させることになる。インピーダンスを下げるためには、ノイズ発生源の電源端子の直近にデカップリングコンデンサ(バイパスコンデンサ/パスコン)を配置する( 「図17 デカップリングコンデンサ」 )。

デカップリングコンデンサは、負荷の電流変化を吸収し、電源電圧の変動やノイズの発生を防止する。デカップリングコンデンサの配置によっては、僅かに配線が残りインダクタンスも残る。インダクタンスの影響を最小化するためには、この配線を極力太く短くする必要がある。

デカップリングコンデンサは負荷のノイズ発生を抑えると共に、負荷の電源に発生した高周波電流を負荷とデカップリングコンデンサの間に封じ込める役割を果たす。ノイズの給電線への拡散を防止するために、フェライトビーズ等の電源用フィルタを挿入する場合もある。

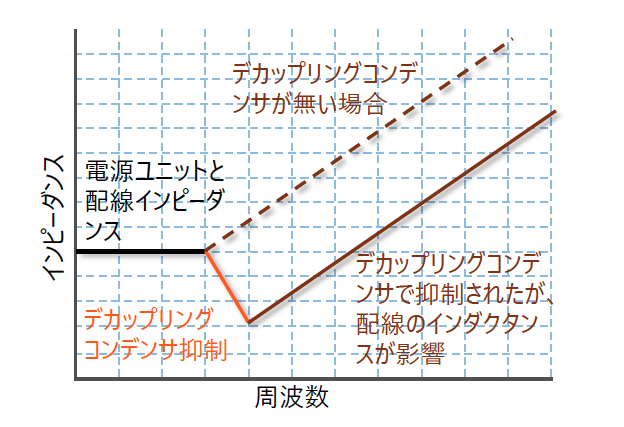

周波数の低い領域では、配線インダクタンスの影響が少ないため平坦な特性になる。デカップリングコンデンサの挿入で、インピーダンスは低下するが、周波数が高くなると配線のインダクタンスの影響が強く(支配的)なり、再びインピーダンスは上昇する( 「図18 電源インピーダンスの周波数特性」 )。

破線部は、デカップリングコンデンサを挿入しない場合の、インピーダンス特性。

電源はノイズの流入や流出の経路だけではなく、デジタル IC に電流を供給する重要な役目がある。電源用フィルタはノイズの流入や流出経路を遮断する目的がある。このフィルタにはキャパシタとインダクタによるローパスフィルタを使用する。

キャパシタはインピーダンスを下げ、インダクタはインピーダンスを上げる方向に働く。高性能なキャパシタは、電源電圧の変動を抑え、放射ノイズも減少する。インダクタはノイズの流入や流出を抑えるが、電源電圧の変動が増える( 「図19 電源電圧変動」 )。

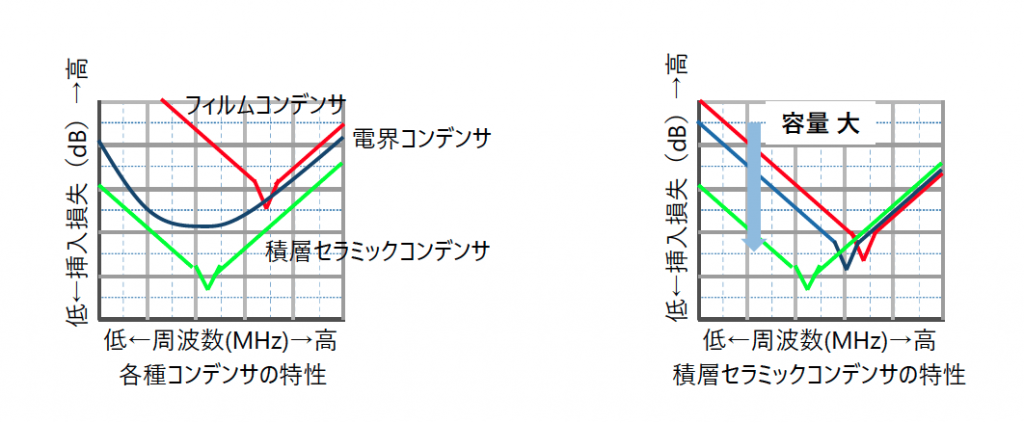

デジタル IC のノイズ対策にインダクタを使用する場合は、組み合わせるキャパシタの容量を十分大きくすることで対応する必要がある。しかし、容量の大きいキャパシタは周波数特性に難があるため、周波数特性の良い容量の小さいキャパシタと併用することもある。

デカップリングコンデンサは一般的には積層セラミックコンデンサだ。セラミックコンデンサは一般的に容量が大きいほど挿入損失が大きい( 「図20 デカップリングコンデンサ特性」 )。キャパシタは低周波領域では挿入損失が大きくノイズフィルタとして働くが、周波数の高い領域では「インダクタンス」として機能しノイズフィルタとして機能しない。このため、極力配線等に含まれるインダクタンスを少なくする必要がある。

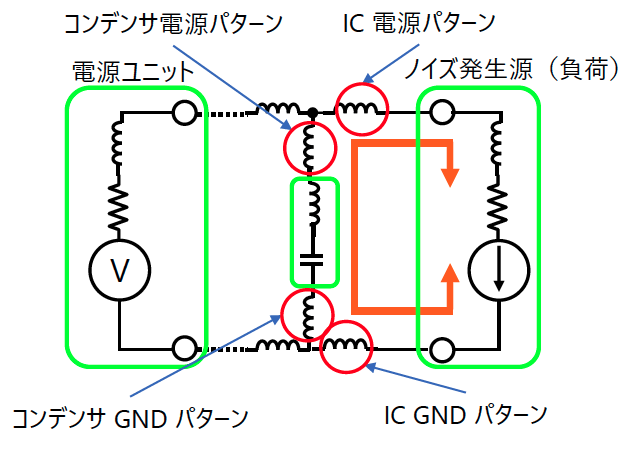

ループインピーダンス

電源配線のインピーダンスは、電源、負荷(デジタル IC )、デカップリングコンデンサとプリント基板パターンで構成される( 「図21 ループインピーダンス」 )。全体のインピーダンスはこれらを一周する電流経路の合計値になる。全体のインダクタンスを下げるためには、プリント基板配線を「太く」 「短く」することが最も効果的だ( 「図22 ループインピーダンス等価回路」赤丸)。もちろん、内部インダクタンスの小さいデカップリングコンデンサを使用するが、プリント基板での対処が効果的だ。

EMC対策

-

2-6.EMI対策

2-6.EMI対策

高周波基板設計の基礎(1)電磁波ノイズ「EMC」の定義

電子機器はノイズ(電磁波)を発生し外部機器に影響を与えると共に、外部機器ノイズの影響を受ける。電子機器が発生するノイズが他の機器に影響を与えないことと、他の機器が発生するノイズに影響されないことの両方の特性を持つ必要があ […] -

2-6.EMI対策

2-6.EMI対策

高周波基板設計の基礎(2)電磁波ノイズ発生の仕組み 「ノイズ発生/ノイズ伝導」

空間に放射されるノイズは、ノイズ発生源→伝送路→アンテナと伝搬し、外部に電磁波として放出される( 「図1 放射ノイズ発生原理」 )。放出された電磁波は他の機器の動作を妨害する。逆に、他の機器から放射された電磁波はこの逆ル […] -

2-6.EMI対策

2-6.EMI対策

高周波基板設計の基礎(3)電磁波ノイズ発生の仕組み「ノイズ反射」

ノイズ反射 半導体デバイス等で発生したノイズは、伝送路を通りアンテナから放射される( 「図1 放射ノイズ発生原理」 )。電磁波の放射を抑えるためには、極力アンテナを少なくする(効率を下げる)ことだ。プリント基板のパターン […] -

2-6.EMI対策

2-6.EMI対策

高周波基板設計の基礎(4)電磁波ノイズ発生の仕組み 「ノーマルモード/コモンモード」

ノーマルモード/コモンモード 基本的な動作としては、デジタル IC で発生したノイズは、伝送路を通りアンテナから放射される。しかし、実際のノイズ対策では、ノイズ発生源が伝送路を介して直接アンテナに繋がることは稀だ。「ノー […] -

2-6.EMI対策

2-6.EMI対策

高周波基板設計の基礎(5)電磁波ノイズ対策・回路 「周波数分離フィルタ」

妨害波対策の基本的な考え方は、「上流工程」での対応を優先することだ。「下流工程」での対応は効果が少なく、対応コストと製造コストが高くなる傾向がある(図1 開発工程)。妨害波ノイズ対策は、プリント基板や筐体も「回路の一部」 […] -

2-6.EMI対策

2-6.EMI対策

高周波基板設計の基礎(6)電磁波ノイズ対策・回路 「信号線でのノイズ対策」

信号線でのノイズ対策に使用するフィルタ 信号線では、信号の高調波を取り除くことがノイズ対策の基本だ。信号線の高調波を取り除くと、デジタル信号の立上り/立下りが遅れ、タイミング設計が難しくなる。電源線では電圧変動を招く恐れ […] -

2-6.EMI対策

2-6.EMI対策

高周波基板設計の基礎(7)電磁波ノイズ対策・回路 「デカップリングコンデンサ / 配線パターン / 配線パターン / ダンピング抵抗 / クロストーク抑制」

デカップリングコンデンサ 最近の半導体は高速化している。同時スイッチング等で、充放電電流が増加し、消費電流の変動が大きくなっている。この電流変動は EMI の要因になる。周波数特性に応じたデカップリングコンデンサの配置が […] -

2-6.EMI対策

2-6.EMI対策

高周波基板設計の基礎(8)電磁波ノイズ対策・回路 「スクランブル」

スクランブル スクランブラは、100Mbps 以上の撚対線を使用する Ethernet 動作時に、コネクタやケーブルから放射する電磁妨害波(EMI)を抑えるために実装された機能だ。電磁妨害波が他の機器の誤動作を引き起こす […] -

2-6.EMI対策

2-6.EMI対策

高周波基板設計の基礎(9)電磁波ノイズ対策・回路 「部品選択」

部品選択 デジタルIC 最も低速なICを選択する4000シリーズ>74HC>74AC>74VHC:高速デジタル IC ほど速度が速く立上りが速い。高調波による放射レベルが大きくなる。低電圧デバイスを選択する電圧変化と電流 […] -

2-6.EMI対策

2-6.EMI対策

高周波基板設計の基礎(10)電磁波ノイズ対策・筐体「シールド/ガスケット」

筐体はノイズシールドとしての役目もあり、ノイズの空間伝導をシールドで遮断する。シールドは回路の一部やケーブルを覆うように使用する場合や、筐体のように装置全体を覆うシールドとして使用する場合等がある。筐体はもちろん、回路の […] -

2-6.EMI対策

2-6.EMI対策

高周波基板設計の基礎(11)電磁波ノイズ対策・筐体「RF 基準面」

プリント基板の GND と筐体(導体)が近づくほど周辺電磁界が少なくなる。この間隔が 1/2 波長より広くなると放射電磁界が増える傾向にある。間隔が 5mm の場合、周波数は 30GHz になり VCCI の測定範囲(3 […] -

2-6.EMI対策

2-6.EMI対策

高周波基板設計の基礎(12)まとめ

EMC は、回路設計部門や筐体設計部門だけの問題ではない。組織全体での取り組みが必要だ。ソフトウェア開発部門は、EMC に最適なパラメータ設定やテストモードの準備が必要だ。製造部門は製造性やコスト確認を行う必要がある。品 […]