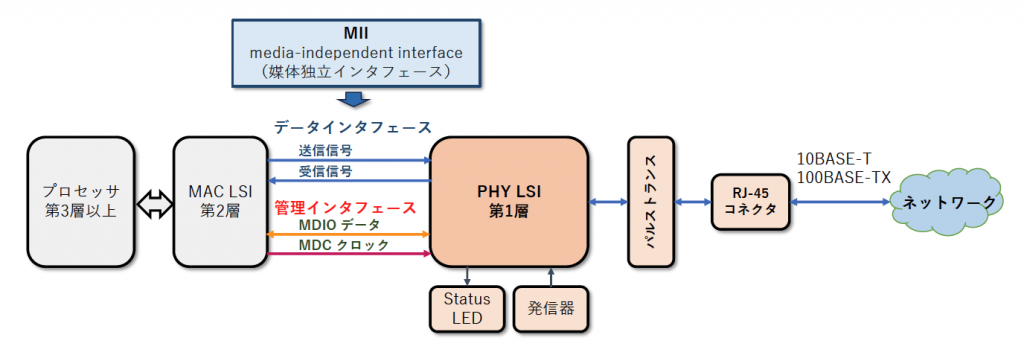

オリジナルの MII は、データインタフェースと管理インタフェースの2つのインタフェースで構成される。データインタフェースは、更に送信用と受信用の2つの独立したチャンネルに分かれる。各チャンネルにはそれぞれ独自のデータ、クロックと制御信号がある。送信用(MAC→PHY)には7本の信号線、受信用(PHY→MAC)には9本の信号線がある。合計16本と信号線が多いインタフェースだ。

管理インタフェースは、1本の双方向データ(MDIO)と1本のクロック(MDC)で構成される。こちらは信号線が2本とシンプルだ。管理インタフェースは、イーサネットの拡張に伴い機能拡張しているが、基本形は変わらず現在も使用されている。MII は IEEE802.3u で規定されている。

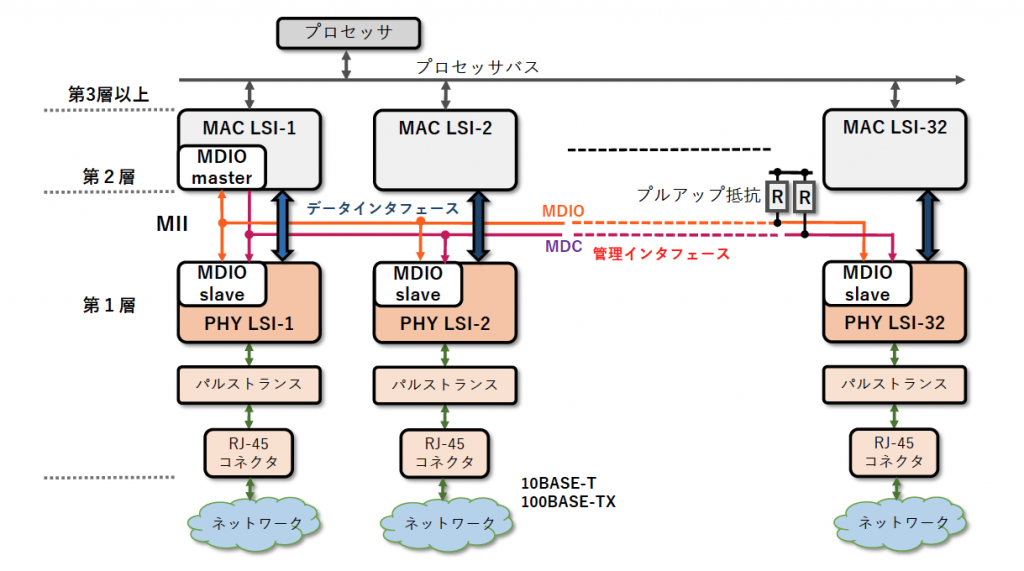

図1 は、イーサネット回路モデルで、第2層の MAC と第1層の PHY 間は MII で接続される。図2 は、スイッチ(ブリッジ)の回路モデルだ。MII のデータインタフェースは、MAC と PHY 間を1対1で接続し、管理インタフェースは最大32個の PHY を一つの MAC 配下に接続することができる。この構成は一見良さそうに見えるが、32ポートスイッチでは MAC と PHY の間に512本のデータインタフェース配線が必要になる。プリント基板のレイアウトはかなり面倒だ。

データインタフェース

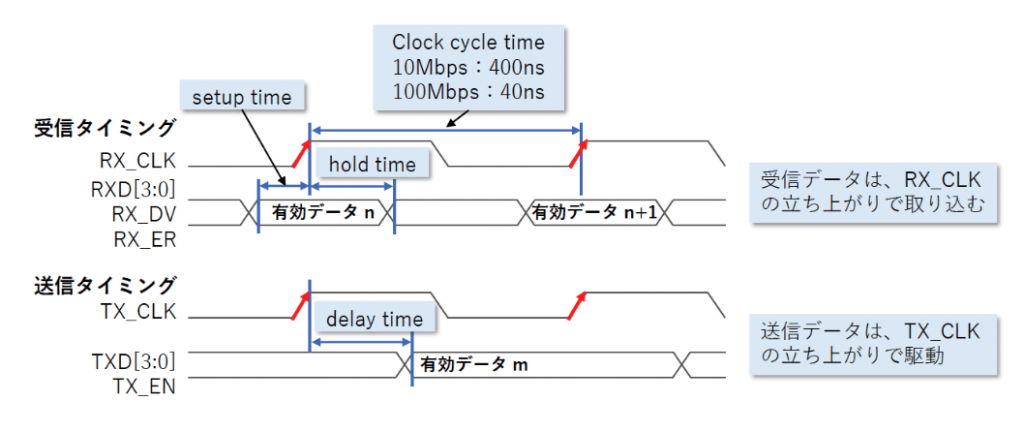

MII データインタフェースには、送信用と受信用にクロックと4ビット幅データバスがある。送信用と受信用クロックは、リンク速度が 100Mbps では 25MHz 、10Mbps では 2.5MHz のクロックが PHY から MAC に供給される。PHY がリンク速度に応じたクロックを供給することで、MAC はリンク速度を意識せずに動作することができる。リンク速度とクロックの関係は次のようなっている。

- 10Mbps :2.5MHz×4bit=10Mbps

- 100Mbps :25MHz×4bit=100Mbps

MII データインタフェースには、データバスとクロック以外に幾つかの制御信号がある。詳細は、表1/表2 をご覧いただきたい。受信データは受信クロックの立ち上がりで取り込み、送信データは送信クロックの立ち上がりクロックで駆動される。図3 は、MII データインタフェースのタイミング例だ。設計時は半導体のマニュアルを参照いただきたい。

| 信号名 | 機能 | 概要 | 信号方向 |

|---|---|---|---|

| TX_CLK | 送信クロック | リンク速度に基づきPHYが生成 ( 100Mbps:25MHz/10Mbps:2.5MHz) | PHY to MAC |

| TXD[3:0] | 送信データビット0 先頭 | MAC がTX_CLKの立ち上がりに同期し駆動。 TXD[0] が先頭ビット | MAC to PHY |

| TX_EN | 送信可 | MAC がTX_CLKの立ち上がりに同期し駆動。 フレーム送信中 High | MAC to PHY |

| TX_ER | 送信エラー(option) | MAC がTX_CLKの立ち上がりに同期し駆動 フレーム内:フレーム送信中止要求/フレーム外:低電力移行要求 | MAC to PHY |

| 信号名 | 機能 | 概要 | 信号方向 |

|---|---|---|---|

| RX_CLK | 受信クロック | リンク速度に基づきPHYが生成 ( 100Mbps:25MHz/10Mbps:2.5MHz) | PHY to MAC |

| RXD[3:0] | 受信データビット0 先頭 | PHY がRX_CLKの立ち上がりに同期し駆動。 RXD[0] が先頭ビット | PHY to MAC |

| RX_DV | 受信データ有効 | PHY がRX_CLKの立ち上がりに同期し駆動 プリアンブル受信後SFD以前にHighに移行。 幾つかのプリアンブル消失の可能性あり | PHY to MAC |

| RX_ER | 受信エラー | PHY がRX_CLKの立ち上がりに同期し駆動 フレーム内:受信エラー/フレーム外:リンク先が低電力モード | PHY to MAC |

| CRS | キャリア検出 | 受信クロックと非同期/半2重モードでのみ有効。 メディア使用中 High | PHY to MAC |

| COL | 衝突検出 | 受信クロックと非同期/半2重モードでのみ有効。 衝突検出で High | PHY to MAC |

管理インタフェース

管理インタフェース(MDIO:Management Data Input/Output)シリアルバスは、MACとPHYの間で管理情報を転送する MII のサブセットインタフェースで、2本の信号線で構成される(表3)。双方向データバスの MDIO とデータ同期クロック MDC だ。ライト時は MDC 立ち上がりで変化し、リード時は MDC の立ち上がりで読み込む。MDC の最高周波数は 2.5MHz になる。2.5MHz は、 MDIO の1ビット幅が 400ナノ秒以上に決まっているためだ。しかし、最近は高速化が進み MDC が 25MHz の製品も流通している。

| 信号名 | 機能 | 概要 | 信号方向 |

|---|---|---|---|

| MDIO | 管理データ | PHY ステータス読出し/設定書込みデータ | 双方向 |

| MDC | 管理データクロック | MDIO 駆動クロック | MAC to PHY |

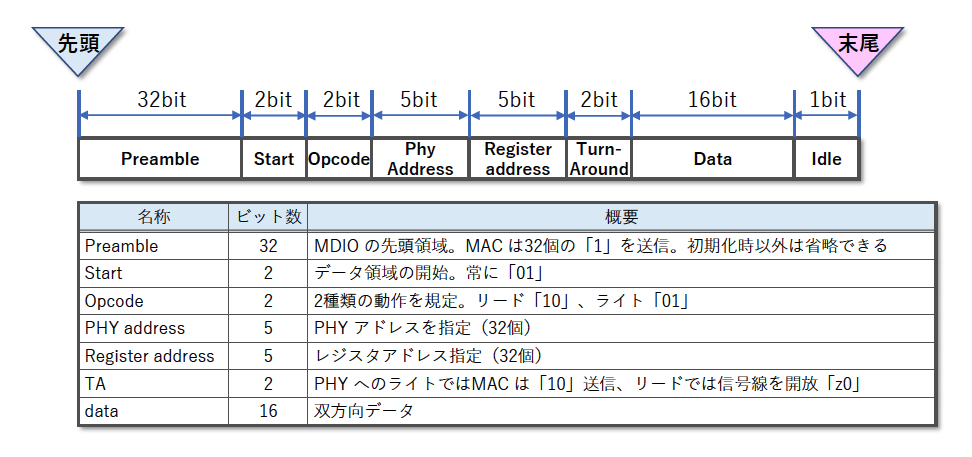

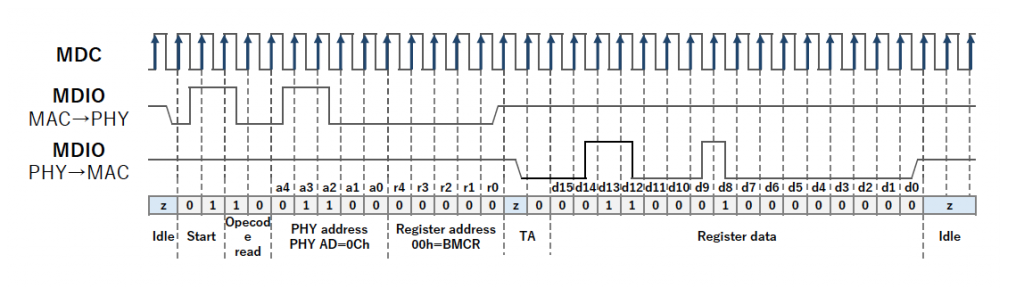

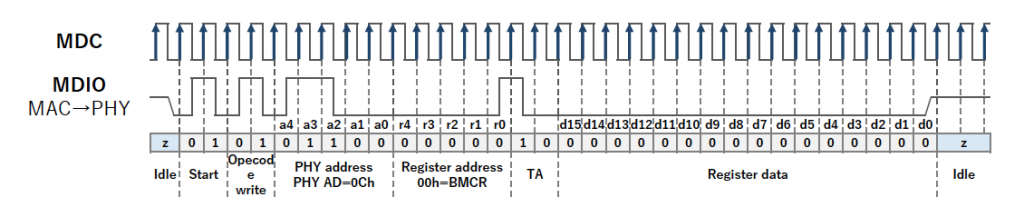

管理インタフェースは、32個の PHY デバイスの最大32個のレジスタにアクセスできる。このレジスタは、リンク状態、通信速度やオートネゴシエーションの起動などの機能がある。図4 は管理インタフェースの基本フォーマットで、図5 はリード動作例、図6 はライト動作例だ。

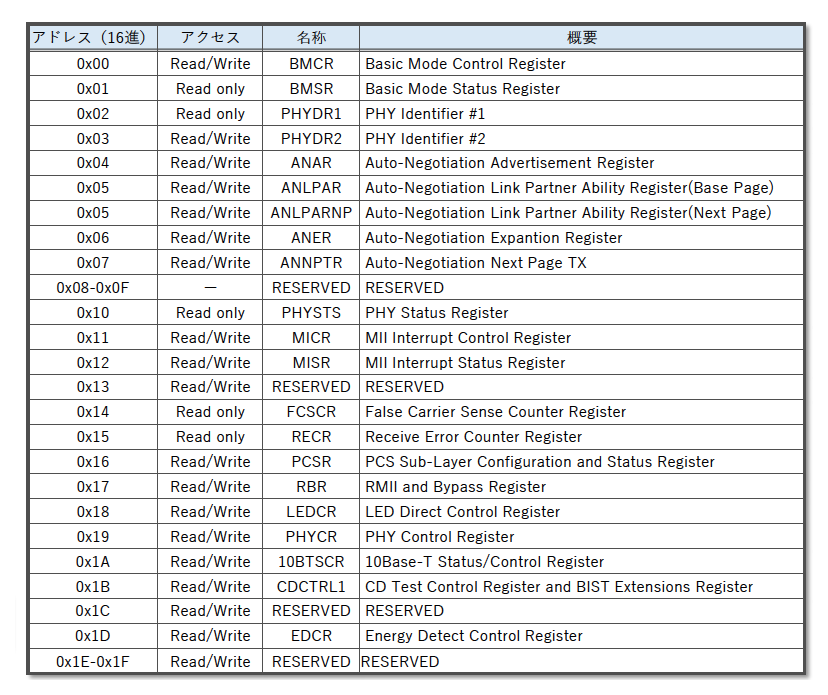

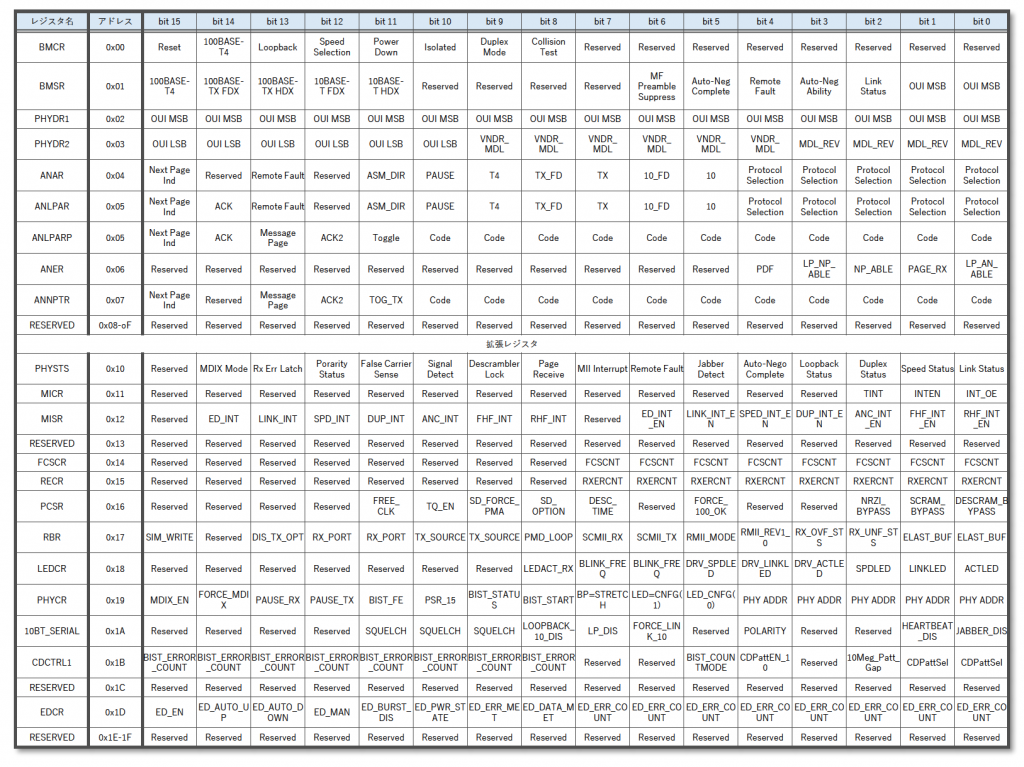

図7 と図8 は、 TEXAS INSTRUMENTS 社の DP83848 の例だ。実際の設計時は最新の半導体マニュアルを参照いただきたい。MII 以外のインタフェース追加や 1Gbps/10Gbps などの高速インタフェースの追加に伴い常に変化しているためだ。

イーサネットの物理層

-

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(1)概要・物理層のトレンド・物理層基礎技術

イーサネットを底辺で支えているのが物理層だ。物理層の基本機能は、0と1で表現されるデジタルデータを電気信号や光パルスに変換し媒体を介して通信することだ。OSI 階層では最下層に相当する。第2層以上の論理層と最下層の物理層 […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(2)物理層基礎技術 パラレル通信とシリアル通信 / クロック同期方式

パラレル通信とシリアル通信 コンピュータ間通信方式はパラレル通信とシリアル通信に大別することができる。パラレル( parallel:並列)通信は、複数データを並列に同時送信するため高速通信が可能だが、複数のデータ線が必要 […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(3)物理層基礎技術 クロック同期方式 共通クロック(Common Clock)同期 / 送信元クロック(Source Clock)同期

共通クロック(Common Clock)同期 プリント基板内での半導体デバイス間同期や、比較的低速な PCI などのパラレルバスで使用されている方式だ。歴史も古く事例も多い。名前のように送信側と受信側が、共通クロックに同 […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(4)物理層基礎技術 クロック同期方式 埋込クロック(Embedded Clock)同期 / 非同期(調歩同期)

埋込クロック(Embedded Clock)同期 「埋込クロック同期」は、送信データに送信クロックを埋め込む方式だ。受信側は受信データからクロックを抽出しデータを読み込むマスタークロックとして使用する。送信元クロック同期 […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(5)物理層基礎技術 DC結合・AC結合

装置間、基板間や基板内回路の電気信号接続には2つの方法がある。直流成分を送ることができる「DC 結合」と、直流成分をカットして交流成分のみを送る「AC 結合」がある。直流成分の除去にはコンデンサやパルストランスを使用する […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(6)全体階層構造

Ethernet TSN は第2層(データリンク層)を主に機能強化している。同時に、車載ネットワークを意識した第1層(物理層)にも新たな規約を策定した。車載ネットワークでは省スペースと重量削減が大きな課題で、これに対応す […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(7)xMII

MII は 10Mbps/100Mbps 専用のインタフェースとして登場した。イーサネットの速度アップに伴い、 MII を基に RMII/GMII/RGMII/SGMII/QSGMII/XGMII などの新たな規格が登場 […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(8)MIIのデータインターフェイス/管理インターフェイス

オリジナルの MII は、データインタフェースと管理インタフェースの2つのインタフェースで構成される。データインタフェースは、更に送信用と受信用の2つの独立したチャンネルに分かれる。各チャンネルにはそれぞれ独自のデータ、 […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(9)xMII RMII / GMII

RMII RMII(Reduced Media-Independent Interface )は、PHY/MAC 間接続の信号線を削減するために作られた規格だ。データインタフェース信号線の総数は16本から半分の8本に削減 […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(10)xMII RGMII / SGMII

RGMII RGMII( Reduced Gigabit Media-Independent Interface )は、 GMII の PHY/MAC 間接続の信号線を削減するために作られた規格だ。信号線の総数は24本か […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(11)物理層規格の概要

イーサネットは40年以上に渡り規格が追加・修正された歴史がある。10Mbps の 10BASE5 から始ま り、400Gbpsまで拡張されている。今回は、IoT や車載ネットワークでの直近の使用が想定される 10Mbps […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(12)物理層規格 10BASE5/2/-T

オフィスでも家庭でも、10BASE5/2/-T 規格の製品に出会うことはまずない。オフィスや家庭での有線イーサネットの主役は 100Mbps か 1000Mbps だ。10BASE5/2/-T 規格は歴史の彼方に消えてい […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(13)個別規格 10BASE5/2/-T 符号化/マンチェスタ符号

符号化 物理層の基本機能は、1と0で表現されるデジタルデータを電気信号に変換しケーブルに流すことだ。最も簡単な変換は、「1」を電圧のハイレベル(例えば5V)に、「0」を電圧のローレベル(例えば 0V)に変換すれば、信号を […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(14)個別規格 100BASE-TX

100BASE-TX は、10BASE-T の次世代規格として1995年に登場した。家庭やオフィス LAN の主役は WiFi や 1000BASE-T に変わったが、今でも広く使われている。100BASE-TX は19 […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(15)個別規格 100BASE-TX 4B5B変換 / Parallel to Serial 変換

4B5B 変換 従来の 10BASE5/2/-T は、伝送路上のフレーム間ギャップは無信号状態になっている。これは、1本の伝送路を複数ノードで共有する方式のため、信号の衝突を避けるためにはデータを送信していない期間を無信 […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(16)個別規格 100BASE-TX スクランブラ / NRZ → NRZI → MLT3 変換

100BASE-TX スクランブラ スクランブラは、100BASE-TX が動作時にコネクタやケーブルから放射する妨害波(EMI)を抑えるために実装された機能だ。「埋込クロック同期」や「AC 結合」のための機能ではない。 […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(17)個別規格 100BASE-FX

100BASE-FX 100BASE-FX は、1995年に IEEE802.3u で標準化された。光ファイバーを伝送路として2本のファイ バーケーブルを使用する。信号源に1300nm波長帯を使い、マルチモードファイバー […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(18)個別規格 1000BASE-T 概要

1000BASE-T は、10BASE-T/100BASE-TX の後継規格として 1999年に IEEE 802.3ab として標準化された。伝送媒体はカテゴリ5以上の撚対線を使用し、最大伝送距離は 100m だ。当時 […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(19)個別規格 1000BASE-T 物理層 / 8B1Q4/4D-PAM5 / スクランブラ

1000BASE-T 1000BASE-T 物理層 1000BASE-T は 8ビット幅を持ち 125MHz(8ナノ秒サイクル)で動作する GMII で上位層と繋がっている。つまり、1000BASE-T の物理層は、8ナ […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(20)個別規格 1000BASE-T 畳み込み符号 / 4D-PAM5 符号 / フレーム構造

1000BASE-T 畳み込み符号 送信データのスクランブル後、8ビットデータに1ビット付加し9ビットにする。変換テーブルに 2倍の冗長性を持たせることと、変換テーブルでデータを拡散し電磁妨害波を抑えることが 1 ビット […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(21)個別規格 1000BASE-X 概要

伝送媒体に光ファイバーを使用する 1000BASE-X は、撚対線を使用する 1000BASE-T より1年早く1998年に標準化を完了している。同時にギガビットイーサに対応する GMII の標準化も完了した。1000B […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(22)個別規格 1000BASE-X 8B/10B 符号化 / 8B10B 変換

8B/10B 符号化 10ビットデータに変換する際に、 1/0 連続数を制限し確実な信号反転を発生させることと 1/0 個数の差を制限制限範囲内に収める必要がある。1/0 連続数制限は、1/0 の連続数が 4 個以内に収 […]