RGMII

RGMII( Reduced Gigabit Media-Independent Interface )は、 GMII の PHY/MAC 間接続の信号線を削減するために作られた規格だ。信号線の総数は24本から半分の12本に削減されている。構造は MII/GMII と変わらず、データインタフェースと管理インタフェースの2つのインタフェースで構成される。データインタフェースは、更に送信用と受信用の2つの独立したチャンネルに分かれる。管理インタフェースはオリジナルの MII と全く同じだ。RGMII は、BROADCOM、Hewlett-Packard、 MARVEL の3社で技術仕様書を発表しているが、IEEE の規格にはなっていない。

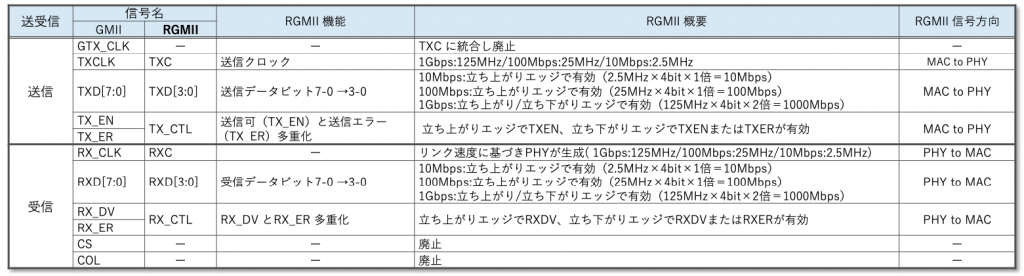

図1 は GMII と RGMII の比較表だ。GMII と RGMII の違いは、送受信データバスを MII と同じ4 ビットに減らしたことだ。10/100Mbps では MII と変わらず、4ビットデータをクロックの立ち上がりで送受信する。1000Mbps ではデータバス幅は 1/2 になったが、クロックの立上りと立下りの両エッジで送受信を行うことでクロックを実質2倍に高速化している。データバス幅は 1/2 になったが、クロックが2倍にすることで GMII と同転送速度を実現している。クロックの立上りと立下りの両エッジを使い方式を DDR(Double Data Rate)と呼ぶ。

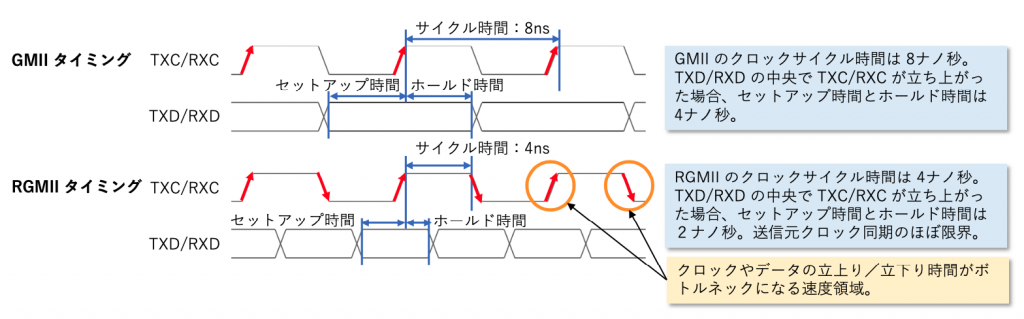

図2 は GMII と RGMII のクロックとデータとのタイミング例だ。GMII は 125MHz クロックの立上りでデータを駆動するため、1サイクルは 8ナノ秒になる。クロックの立上りがデータの中央であれば、セットアップ時間とホールド時間はいずれも 4ナノ秒を確保できる。GMII/RGMII の半導体に必要なセットアップ時間とホールド時間は 1~2ナノ秒であることを考えると、実現できる範囲だ。 RGMII はクロックの両エッジを使用するため、1サイクルは半分の僅か 4ナノ秒になる。クロックの変化がデータの中央であっても、セットアップ時間とホールド時間は 2ナノ秒になり、半導体に必要な時間とほぼ一致する。例えば Texas Instruments 社の RGMII 半導体では、最小セットアップ/ ホールド時間は 1.2ナノ秒になっている。理想的な場所でクロックが変化しても、残されたマージンは僅か 0.8ナノ秒に過ぎない。

RGMII 半導体では、この微妙な時間を調整するため遅延調整ができるようになっている。このような厳しいタイミングを実現するためには、クロックやデータの立上り/立下り時間が問題になる。この時間を短くするため、駆動電圧が低く立上り/立下り時間が短い半導体を順次採用している。例えば、 RGMII Version1.3 では 2.5V CMOS、RGMII Version2 では 1.5V HSTL を採用している。

SGMII

SGMII( Serial Gigabit Media-Independent Interface )は、MII と同様 MAC と PHY 間接続のインタフェース規格だ。本来は 1000Mbps 用だが、10/100Mbps にも適用できる。基本構造は MII と変わらず、データインタフェースと管理インタフェースの2つのインタフェースで構成される。データインタフェース構造は MII とは異なり 1ビット単位のシリアル伝送で、データ送信用差動信号(TX+ /TX-)データ受信用差動信号(RX+/RX-)、送信データ用差動クロック(TXCLK+/TXCLK-)と受信用差動クロック(RXCLK+/RXCLK-)の8本で構成される(表1/2)。データ送受信用クロックは、何れも 625MHz 固定でクロックの両エッジ(立上り/立下り)で同期をとる DDR 方式だ。実質的なクロックは 1.25GHz になる。

| 信号名 | 機能 | 概要 | 信号方向 |

|---|---|---|---|

| TX+ | 送信データ | 送信データ(差動信号+) | MAC to PHY |

| TX- | 送信データ | 送信データ(差動信号ー) | MAC to PHY |

| RX+ | 受信データ | 送信データ(差動信号+) | PHY to MAC |

| RX- | 受信データ | 送信データ(差動信号ー) | PHY to MAC |

| 信号名 | 機能 | 概要 | 信号方向 |

|---|---|---|---|

| TXCLK+ | 送信クロック | 送信クロック(差動信号+) | MAC to PHY |

| TXCLK- | 送信クロック | 送信クロック(差動信号ー) | MAC to PHY |

| RXCLK+ | 受信クロック | 受信クロック(差動信号+) | PHY to MAC |

| RXCLK- | 受信クロック | 受信クロック(差動信号ー) | PHY to MAC |

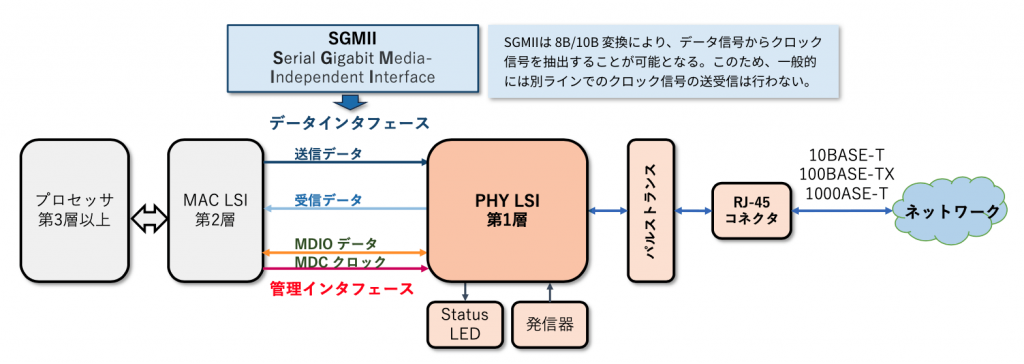

送受信データは、SerDes と呼ばれる 8B/10B 変換(8ビットを10ビットに変換)を行うため、データ量は 1.25倍になる。データ量が 1.25倍に増えているが、実質クロックが 1.25GHz であるため 1000Mbps の性能を実現することができる。10/100Mbps では、データをそれぞれ 100/10 回複製することで互換性を取っている。SGMII の MAC/PHY 間接続は図3 で、MII や GMII と同じ構成になる。管理インタフェース(MDIO/MDC)に変更はない。

SGMII は、元々 Cisco 社の独自規格だが、様々なベンダーが SGMII に対応し事実上の業界標準に なっている。Cisco 社は「Serial-GMII Specification」として仕様を公開し、これに関連する権利を放棄している。SGMII は IEEE の規格にはなっていない。

SerDes とは?

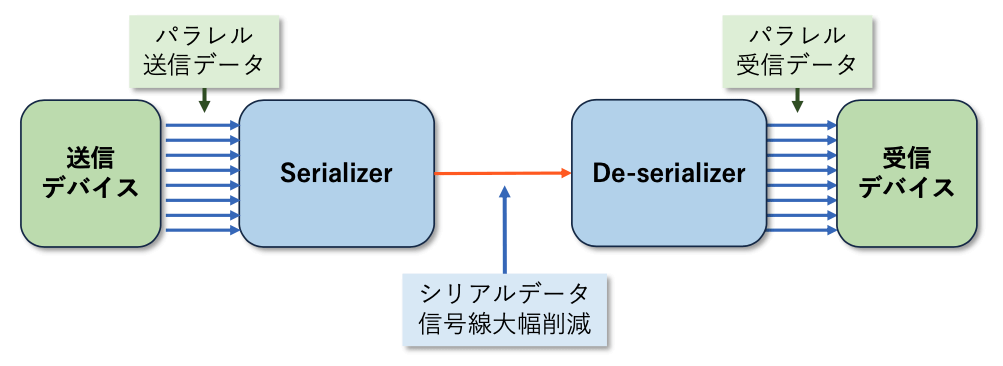

SerDes(サーデス)は、Serializer と De-serializer の合成語だ。 Serializer はパラレルデータ入力を 1本のシリアルデータに変換する「パラシリ」変換で、 De-serializer はシリアルデータを元のパラレルデータに戻す「シリパラ」変換だ。この技術はイーサネット特有の技術ではなく、PCI Express や USB 等で広く使われている汎用技術だ。信号線を削減しノイズ低減やコスト削減に有効だ。動作イメージは図4 を参照いただきたい。

イーサネットの物理層

-

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(1)概要・物理層のトレンド・物理層基礎技術

イーサネットを底辺で支えているのが物理層だ。物理層の基本機能は、0と1で表現されるデジタルデータを電気信号や光パルスに変換し媒体を介して通信することだ。OSI 階層では最下層に相当する。第2層以上の論理層と最下層の物理層 […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(2)物理層基礎技術 パラレル通信とシリアル通信 / クロック同期方式

パラレル通信とシリアル通信 コンピュータ間通信方式はパラレル通信とシリアル通信に大別することができる。パラレル( parallel:並列)通信は、複数データを並列に同時送信するため高速通信が可能だが、複数のデータ線が必要 […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(3)物理層基礎技術 クロック同期方式 共通クロック(Common Clock)同期 / 送信元クロック(Source Clock)同期

共通クロック(Common Clock)同期 プリント基板内での半導体デバイス間同期や、比較的低速な PCI などのパラレルバスで使用されている方式だ。歴史も古く事例も多い。名前のように送信側と受信側が、共通クロックに同 […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(4)物理層基礎技術 クロック同期方式 埋込クロック(Embedded Clock)同期 / 非同期(調歩同期)

埋込クロック(Embedded Clock)同期 「埋込クロック同期」は、送信データに送信クロックを埋め込む方式だ。受信側は受信データからクロックを抽出しデータを読み込むマスタークロックとして使用する。送信元クロック同期 […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(5)物理層基礎技術 DC結合・AC結合

装置間、基板間や基板内回路の電気信号接続には2つの方法がある。直流成分を送ることができる「DC 結合」と、直流成分をカットして交流成分のみを送る「AC 結合」がある。直流成分の除去にはコンデンサやパルストランスを使用する […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(6)全体階層構造

Ethernet TSN は第2層(データリンク層)を主に機能強化している。同時に、車載ネットワークを意識した第1層(物理層)にも新たな規約を策定した。車載ネットワークでは省スペースと重量削減が大きな課題で、これに対応す […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(7)xMII

MII は 10Mbps/100Mbps 専用のインタフェースとして登場した。イーサネットの速度アップに伴い、 MII を基に RMII/GMII/RGMII/SGMII/QSGMII/XGMII などの新たな規格が登場 […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(8)MIIのデータインターフェイス/管理インターフェイス

オリジナルの MII は、データインタフェースと管理インタフェースの2つのインタフェースで構成される。データインタフェースは、更に送信用と受信用の2つの独立したチャンネルに分かれる。各チャンネルにはそれぞれ独自のデータ、 […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(9)xMII RMII / GMII

RMII RMII(Reduced Media-Independent Interface )は、PHY/MAC 間接続の信号線を削減するために作られた規格だ。データインタフェース信号線の総数は16本から半分の8本に削減 […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(10)xMII RGMII / SGMII

RGMII RGMII( Reduced Gigabit Media-Independent Interface )は、 GMII の PHY/MAC 間接続の信号線を削減するために作られた規格だ。信号線の総数は24本か […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(11)物理層規格の概要

イーサネットは40年以上に渡り規格が追加・修正された歴史がある。10Mbps の 10BASE5 から始ま り、400Gbpsまで拡張されている。今回は、IoT や車載ネットワークでの直近の使用が想定される 10Mbps […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(12)物理層規格 10BASE5/2/-T

オフィスでも家庭でも、10BASE5/2/-T 規格の製品に出会うことはまずない。オフィスや家庭での有線イーサネットの主役は 100Mbps か 1000Mbps だ。10BASE5/2/-T 規格は歴史の彼方に消えてい […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(13)個別規格 10BASE5/2/-T 符号化/マンチェスタ符号

符号化 物理層の基本機能は、1と0で表現されるデジタルデータを電気信号に変換しケーブルに流すことだ。最も簡単な変換は、「1」を電圧のハイレベル(例えば5V)に、「0」を電圧のローレベル(例えば 0V)に変換すれば、信号を […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(14)個別規格 100BASE-TX

100BASE-TX は、10BASE-T の次世代規格として1995年に登場した。家庭やオフィス LAN の主役は WiFi や 1000BASE-T に変わったが、今でも広く使われている。100BASE-TX は19 […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(15)個別規格 100BASE-TX 4B5B変換 / Parallel to Serial 変換

4B5B 変換 従来の 10BASE5/2/-T は、伝送路上のフレーム間ギャップは無信号状態になっている。これは、1本の伝送路を複数ノードで共有する方式のため、信号の衝突を避けるためにはデータを送信していない期間を無信 […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(16)個別規格 100BASE-TX スクランブラ / NRZ → NRZI → MLT3 変換

100BASE-TX スクランブラ スクランブラは、100BASE-TX が動作時にコネクタやケーブルから放射する妨害波(EMI)を抑えるために実装された機能だ。「埋込クロック同期」や「AC 結合」のための機能ではない。 […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(17)個別規格 100BASE-FX

100BASE-FX 100BASE-FX は、1995年に IEEE802.3u で標準化された。光ファイバーを伝送路として2本のファイ バーケーブルを使用する。信号源に1300nm波長帯を使い、マルチモードファイバー […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(18)個別規格 1000BASE-T 概要

1000BASE-T は、10BASE-T/100BASE-TX の後継規格として 1999年に IEEE 802.3ab として標準化された。伝送媒体はカテゴリ5以上の撚対線を使用し、最大伝送距離は 100m だ。当時 […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(19)個別規格 1000BASE-T 物理層 / 8B1Q4/4D-PAM5 / スクランブラ

1000BASE-T 1000BASE-T 物理層 1000BASE-T は 8ビット幅を持ち 125MHz(8ナノ秒サイクル)で動作する GMII で上位層と繋がっている。つまり、1000BASE-T の物理層は、8ナ […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(20)個別規格 1000BASE-T 畳み込み符号 / 4D-PAM5 符号 / フレーム構造

1000BASE-T 畳み込み符号 送信データのスクランブル後、8ビットデータに1ビット付加し9ビットにする。変換テーブルに 2倍の冗長性を持たせることと、変換テーブルでデータを拡散し電磁妨害波を抑えることが 1 ビット […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(21)個別規格 1000BASE-X 概要

伝送媒体に光ファイバーを使用する 1000BASE-X は、撚対線を使用する 1000BASE-T より1年早く1998年に標準化を完了している。同時にギガビットイーサに対応する GMII の標準化も完了した。1000B […] -

2-5.Ethernetの物理層

2-5.Ethernetの物理層

イーサネットの物理層(22)個別規格 1000BASE-X 8B/10B 符号化 / 8B10B 変換

8B/10B 符号化 10ビットデータに変換する際に、 1/0 連続数を制限し確実な信号反転を発生させることと 1/0 個数の差を制限制限範囲内に収める必要がある。1/0 連続数制限は、1/0 の連続数が 4 個以内に収 […]